# FAD7606 八通道 16 位 200kSPS ADC

#### 产品概述

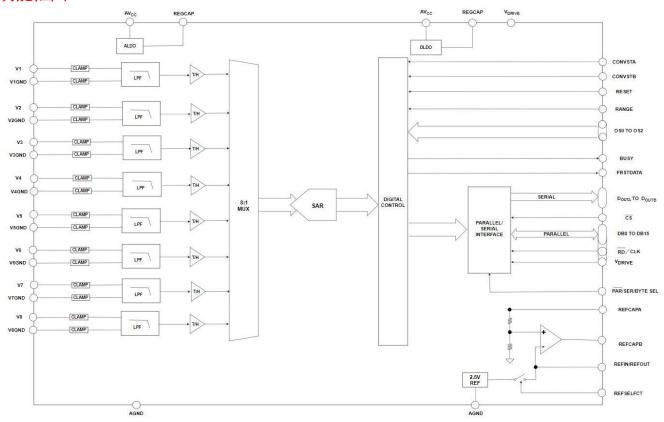

FAD7606 是一款 16 位 8 通道同步采样模数转换器,每个通道均内置模拟输入箝位保护、模拟滤波器、可编程增益放大器。该器件还集成了数字滤波器、3.5 ppm/°C低漂移 2.5V 精密基准电压源和 4.5V 基准电压缓冲器,支持并行和串行接口。

FAD7606 采用5V单电源供电,所有8个通道的吞吐速率均可达 200kSPS,支持±10V和±5V真双极性输入范围,具有 1MΩ 模拟输入阻抗,输入箝位保护可承受高达±30V 的电压, ESD 等级可达8kV。对于吞吐率要求较低的应用, FAD7606 内建的过采样模式和灵活的数字滤波器可用来 改善噪声性能。

#### 主要性能

- 16位、200kSPS(所有通道)

- 具有1MQ 模拟输入阻抗的输入缓冲器

- 工作温度范围: -40°C至+85°C

- 5V单模拟电源

- VDRIVE 电源电压: 2.3V 至 5V

- ±30V 输入箝位保护,8kV ESD

- 2阶抗混叠模拟滤波器

- 片上精密基准源和基准电压源缓冲器

- 真双极性模拟输入范围: ±10V、±5V

- 集成数字滤波器的过采样功能

- SNR 86dB (无过采样) 95dB(64 倍过采样)

- QFP-64 封装 12mm×12mm

## 应用场合

1

- 电力线路监控

- 继电保护

- 多相电机控制

- 仪器仪表和控制系统

- 数据采集系

## 功能框图

## 电气特性

除非另有说明,AVCC=4.75V 至 5.25V、VDRIVE=2.3V 至 5.25V、200kSPS 采样率,单端输入、2.5V内部基准电压。

表 1 电气特性

| 参数          | 条件   | 最小值 | 典型值 | 最大值 | 単位  |

|-------------|------|-----|-----|-----|-----|

| 分辨率         |      |     | 16  |     | 位   |

| 微分非线性 (DNL) | 25°C |     | ±1  |     | LSB |

| 积分非线性(INL)  | 25°C |     | ±1  |     | LSB |

| 输入端阻抗       | 25°C |     | 1   |     | мΩ  |

| 模拟输入范围±10V  |      | -10 |     | 10  | V   |

| 模拟输入范围±5V                | 全 | -5   |    | 5    | V  |

|--------------------------|---|------|----|------|----|

| 输入电容                     |   |      | 5  |      | pF |

| 电源电压(AVCC)               | 全 | 4.75 | 5  | 5.25 | V  |

| 电源电压(VDRIVE)             | 全 | 2.3  |    | 5.25 | V  |

| 电源电流(I <sub>AVCC</sub> ) | 全 |      | 19 |      | mA |

| 参数                                       | 条件      | 最小值 | 典型值  | 最大值 | 単位     |

|------------------------------------------|---------|-----|------|-----|--------|

| 电源电流(I <sub>VDRIVE</sub> )               | 全       |     | 1.4  |     | mA     |

| 正常工作功耗                                   | 全       |     | 102  |     | mW     |

| 待机功耗                                     | 25°C    |     | 15   |     | mW     |

| 关断功耗                                     | 25°C    |     | 1.5  | 25  | μW     |

| 信噪比(SNR) <sup>1</sup> _无过采样<br>(无 OS)    | ±10V 范围 |     | 86   |     | dB     |

| 信噪比(SNR) <sup>1</sup> _过采样率<br>(OSR)=16x | ±10V 范围 |     | 93   |     | dB     |

| 总谐波失真 (THD)                              | 25°C    |     | -102 |     | dB     |

| 无杂散动态范围(SFDR)                            | 25°C    |     | -108 |     | dB     |

| 通道间隔离                                    | 25°C    |     | -92  |     | dB     |

| 输出温漂                                     | 全       |     | ±3.5 |     | ppm/°C |

<sup>1.</sup>测量条件为: 1kHz 输入频率、满量程正弦波。

#### 数字规格

除非另有说明,AVCC=4.75V 至5.25V、VDRIVE=2.3V 至 5.25V、200kSPS 采样率,单端输入、2.5V 内部基准电压。

参数 温度 最小值 典型值 最大值 单位 逻辑输入 0.7xVDRIVE 全 逻辑1电压 V 0 逻辑0电压 全 0.3xVDRIVE V 全  $\pm 1$ 输入电流 μΑ 5 输入电容 全 pF 数字输出 逻辑1 电压 全 VDRIVE-0.2 V 逻辑 0 电压 全 0.2 V 编码格式 (默认) 二进制补码

表 2 数字规格参数

## 时序规格

除非另有说明,AVCC=4.75V 至5.25V、VDRIVE=2.3V 至5.25V、200kSPS 采样率,单端输入、2.5V 内部基准电压。使用 20 pF 负载电容测试接口时序,具体取决于VDRIVE 和串行接口的负载电容。

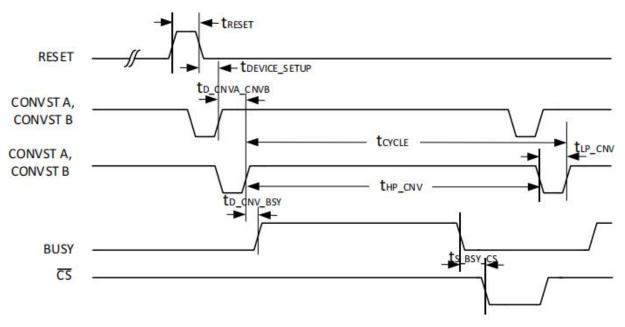

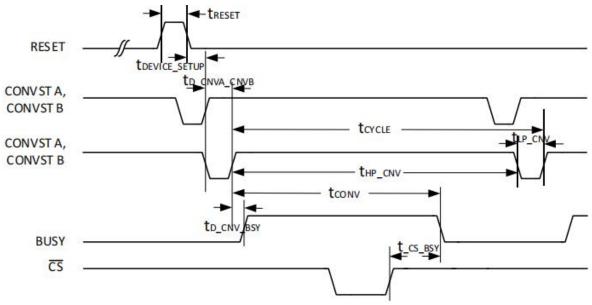

#### 1.通用时序规格

表 3 通用时序规格参数

| 参数                        | 最小值 | 典型值 | 最大值 | 单位 | 描述                             |

|---------------------------|-----|-----|-----|----|--------------------------------|

| tcycle                    |     |     | 5   | μs | 连续CONVST上升沿之间的最短时间(不包括过采样模式)   |

| t <sub>LP_CNV</sub>       | 25  |     |     | ns | CONVST 低电平脉冲宽度                 |

| thp_cnv                   | 25  |     |     | ns | CONVST 高电平脉冲宽度                 |

| t <sub>D_CNV_BSY</sub>    |     |     | 40  | ns | CONVST 高电平至 BUSY 高电平延迟时间       |

| $t_{\mathrm{S\_BSY\_CS}}$ | 0   |     |     | ns | 从 BUSY 下降沿到 CS 下降沿建立时间         |

| td_cnva_cnvb              |     |     | 0.5 | ms | CONVST A 与CONVST B 上升沿之间最大延迟时间 |

| t_cs_bsy                  |     |     | 25  | ns | CS 上升沿到 BUSY 下降沿最大间隔时间         |

| 参数                               | 最小值 典型值 最大值     | 单位             | 描述                                |

|----------------------------------|-----------------|----------------|-----------------------------------|

|                                  | 4               | μs             | 转换时间; 无过采样                        |

|                                  | 9               | μs             | 2 倍过采样                            |

|                                  | 19              | μs             | 4 倍过采样                            |

| t <sub>CONV</sub>                | 39              | μs             | 8 倍过采样                            |

|                                  | 79              | μs             | 16 倍过采样                           |

|                                  | 159             | μs             | 32 倍过采样                           |

|                                  | 319             | μs             | 64 倍过采样                           |

| t <sub>reset</sub>               | 50              | ns             | RESET 高电平脉冲宽度                     |

| tdevice_setup                    | 50              | us             | RESET 下降沿和第一个 CONVST 上升沿之间的时间     |

| t <sub>WAKE_UP</sub><br>待机<br>关断 | 100<br>30<br>13 | Ms<br>ms<br>ms | 待机/关断模式后的唤醒时间<br>内部参考电压<br>外部参考电压 |

注: 上电只需要reset一次即可, 无需重复复位

图 2 转换时序图, 转换后读入数据

图 3 转换时序图,转换期间读入数据

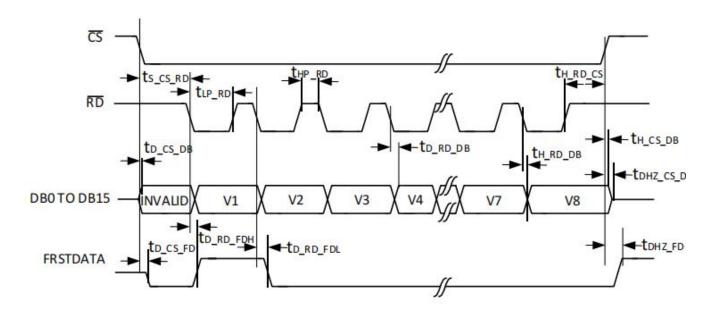

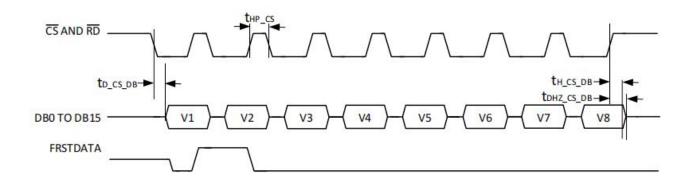

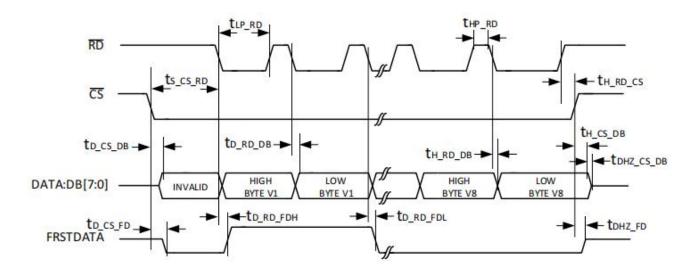

## 2. 并行模式时序规格

表 4 并行模式时序规格参数

| 参数                     | 最小值 | 典型值 | 最大值 | 单位 | 描述                                   |

|------------------------|-----|-----|-----|----|--------------------------------------|

| T <sub>S_CS_RD</sub>   | 0   |     |     | ns | CS 下降沿到 CS 下降沿建立时间                   |

| t <sub>H_RD_CS</sub>   | 0   |     |     | ns | RD 上升沿到 CS 上升沿保持时间                   |

| t <sub>HP_RD</sub>     | 15  |     |     | ns | RD 高电平脉冲宽度                           |

| t <sub>LP_RD</sub>     | 16  |     |     | ns | RD 低电平脉冲宽度                           |

| $t_{\mathrm{HP\_CS}}$  | 22  |     |     | ns | CS 高电平脉冲宽度                           |

| t <sub>D_CS_DB</sub>   |     |     | 16  | ns | 从 CS 到 DBx 三态禁用的延迟时间                 |

| t <sub>H_CS_DB</sub>   | 6   |     |     | ns | CS 到 DBx 保持时间                        |

| t <sub>D_RD_DB</sub>   |     |     | 16  | ns | RD 下降沿后的数据传输时间                       |

| t <sub>H_RD_DB</sub>   | 6   |     |     | ns | RD 下降沿后的数据保持时间                       |

| t <sub>DHZ_CS_DB</sub> |     |     | 22  | ns | CS 上升沿到 DBx 三态使能延迟时间                 |

| t <sub>D_CS_FD</sub>   |     |     | 15  | ns | 从 CS 下降沿到 FRSTDATA 三态禁用的延迟时间         |

| t <sub>D_CS_FDH</sub>  |     |     | 15  | ns | 从CS 下降沿到 FRSTDATA 高电平的延迟时间           |

| td_rd_fdh              |     |     | 16  | ns | 从 CS 下降沿到 FRSTDATA 高电平的延迟时间          |

| t <sub>D_RD_FDL</sub>  |     |     | 19  | ns | 从 RD 下降沿到 FRSTDATA 低电平的延迟时间          |

| t <sub>DHZ_FD</sub>    |     |     | 24  | ns | 从 CS 上升沿到 FRSTDATA 三态使能的延迟时间         |

| t <sub>D_SCK_FDL</sub> |     |     | 17  | ns | 从第 16 次 SCLK 下降沿到 FRSTDATA 低电平的延迟 时间 |

图4并行模式读取时序图,分离的 CS 和 RD 脉冲

图 5 并行模式读取时序图,相连的 CS 和 RD

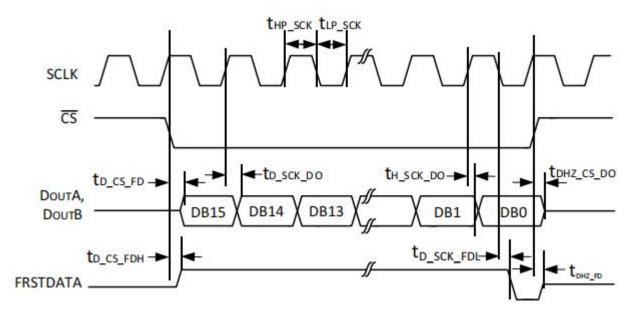

#### 3. 串行模式时序规格

表 5 串行模式时序规格参数

| 参数                     | 最小值 典型值 最大值 | 单位  | 描述                        |

|------------------------|-------------|-----|---------------------------|

| $f_{ m SCLK}$          | 30          | MHz | SCLK 频率;fSCLK = 1/tSCLK   |

| $t_{ m SCLK}$          | 1/fSCLK     | μs  | 最短 SCLK 周期                |

| ts_cs_sck              | 2           | ns  | CS 到 SCLK 下降沿建立时间         |

| t <sub>H_SCK_CS</sub>  | 2           | ns  | SCLK 到 CS 上升沿保持时间         |

| t <sub>LP_SCK</sub>    | 0.4 ×tSCLK  | ns  | SCLK 低电平脉宽                |

| t <sub>HP_SCK</sub>    | 0.4 ×tSCLK  | ns  | SCLK 高电平脉宽                |

| t <sub>DHZ_CS_DO</sub> | 22          | ns  | 从 CS 上升沿到 DOUTx 三态使能的延迟时间 |

| t <sub>D_SCK_DO</sub> |   | 17 | ns | SCLK 上升沿后的 DOUTx 数据传输时间                   |

|-----------------------|---|----|----|-------------------------------------------|

| t <sub>H_SCK_DO</sub> | 7 |    | ns | SCLK 上升沿后的 DOUTx 输出数据保持时间                 |

| t <sub>D_CS_FD</sub>  |   | 15 | ns | 从 CS 到 DOUTx 三态禁用的延迟时间/从 CS 到 MSB 有效的延迟时间 |

图 6 串行时序图, ADC 读取模式 (通道 1)

图 7串行接口时序图,字节模式读操作

## 极限参数

| AVCC 至 AGND                                                                 | V至7V           |

|-----------------------------------------------------------------------------|----------------|

| VDRIVE 至 AGND                                                               | V 至 AVCC +0.3V |

| 模拟输入电压至 AGND                                                                | ±22V           |

| 数字输入电压至 AGND                                                                | V至VDRIVE+0.3V  |

| 数字输出电压至 AGND                                                                | V至VDRIVE+0.3V  |

| 最大结温 TJ,MAX                                                                 | 150°C          |

| 工作温度范围                                                                      | 40°C 至 85°C    |

| 存储温度范围                                                                      | 65°C 至 150°C   |

| ESD(Human Body Model) 除模拟输入外                                                | V              |

| ESD(Human Body Model) 模拟输入                                                  | V              |

| <b>注意:</b> 对以上所列的最大极限值,如果器件工作在超过此极限值的环境中,<br>在实际运用中,最好不要使器件工作在此极限值或超过此极限值的环 |                |

本产品属于静电敏感器件。当拿取时,要采取合适的ESD保护措施,以免造成性能下降或功能 失效。

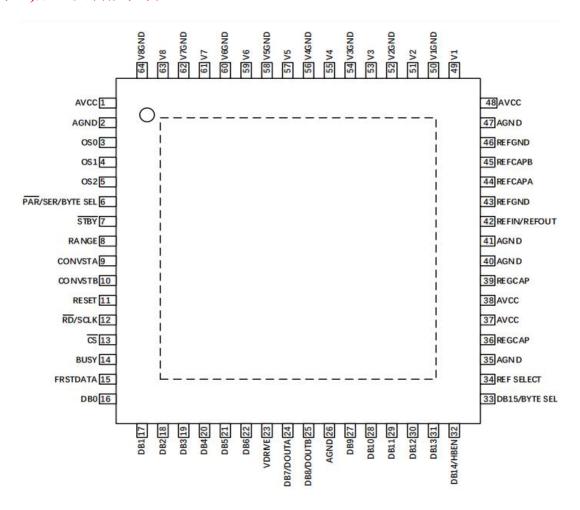

## 管脚(焊盘)配置及功能说明

图 8.8 通道 FAD7606 管脚(焊盘)配置(俯视图)

#### 表 6 管脚定义

| 引脚编号          | 引脚类型 | 引脚名称      |                                           |

|---------------|------|-----------|-------------------------------------------|

| 1, 37, 38, 48 | P    | AVCC      | 模拟电源电压, 4.75V 至 5.25V 。电源引脚去耦至 AGND。      |

| 2, 26,        |      |           |                                           |

| 35, 40,       | G    | AGND      | 模拟地。为片上所有模拟电路的接地点,六个 AGND 引脚均须连接至系统层的地平面。 |

| 41, 47        |      |           |                                           |

| 3 至 5         | DI   | OS0 至 OS2 | 过采样模式引脚。过采样率配置详情参见表 9。                    |

| 6     | DI | PAR /SER/BY<br>TE SEL | 并行/串行接口选择输入。若此引脚为逻辑低电平,选择并行接口输入;若此引脚为逻辑高电平,则选择串行接口输入。详情参见表 8。                                                                                |

|-------|----|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | DI | STBY                  | 电源模式选择。此引脚接逻辑低电平时,配合 RANGE 引脚一起控制可将芯片配置成待机模式或关断模式,详情参见表 7。 电路正常工作时须置为逻辑高电平。                                                                  |

| 8     | DI | RANGE                 | 模拟输入范围选择。电路正常工作下,此引脚决定模拟输入通道的输入范围。若 STBY 引脚处于逻辑高电平,RANGE 为 0 时,输入范围 为±5V; RANGE 为 1 时,输入范围为±10V。若 STBY 引脚处于逻辑低电平,芯片则进入省电模式(待机或关断模式),详情参见表 7。 |

| 9, 10 | DI | CONVSTA<br>CONVSTB    | 转换开始输入信号。当 CONVST A 和 B 引脚从低电平变为高电平时 ADC 开始转换。                                                                                               |

| 11    | DI | RESET                 | 复位输入,高电平有效。在 ADC 转换期间进行 RESET ,则转换终止;在读取期间进行 RESET,则输出寄存器复位为全 0。建议器件上电后先 RESET 一次。                                                           |

| 12    | DI | RD /SCLK              | 并行接口模式时,并行数据读取控制输入(RD)。串行接口模式时,串行时钟输入(SCLK)。                                                                                                 |

| 13    | DI | CS                    | 片选信号。对于串行和并行接口,此引脚均为低电平有效,用于<br>ADC 数据读取或寄存器数据读写。                                                                                            |

| 14    | DO | BUSY                  | 输出忙信号。此引脚随同 CONVSTA 和 CONVSTB 的上升沿变为逻辑高电平。所有通道转换过程完成之前,BUSY 输出保持高电平。                                                                         |

| 15    | DO | FRSTDATA              | 第一个数据输出标志。FRSTDATA输出信号指示何时在并行接口或串行接口上读取第一通道 V1 的数据。                                                                                          |

| 16至22 | DO | DB0 至 DB6             | 并行输出数据位。使用并行接口时,这些引脚用作三态并行数字输入和输出;使用串行接口时,应将这些引脚连接到 AGND。当使用并行字节接口时,DB[7:0]在读两次操作后输出 16 位转换结果。                                               |

| 23    | P  | VDRIVE                | 逻辑电源输入。此引脚的电源电压(2.3V 至 5.25V)为逻辑接口的工作电压。                                                                                                     |

| 24    | DO | DB7/DOUT A            | 并行输出数据位 (DB7)/串行接口数据输出引脚(DOUTA)。使用并行接口时,此引脚用作三态并行数字输入/输出引脚。使用串行接口时,此引脚用作 DOUTA。                                                              |

| 25    | DO | DB8/DOUT B | 并行输出数据位 8(DB8)/串行接口数据输出引脚(DOUTB)。使用并 行接口时,此引脚用作三态并行数字输入/输出引脚;使用串行接口时,此引脚用作 DOUTB。 |

|-------|----|------------|-----------------------------------------------------------------------------------|

| 31至27 | DO | DB[13:9]   | 并行输出数据位 DB13 至 DB9。使用并行接口时,这些引脚用作三态并行数字输入和输出引脚,使用串行接口时,应将这些引脚连接到AGND。             |

| 引脚编号  | 引脚类型  | 引脚名称             | 引脚功能                                                                                                                                                                                                                                              |

|-------|-------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32    | DO/DI | DB14/HBEN        | 并行输出数据位 14(DB14)/高位字节使能(HBEN)<br>当 PAR /SER/BYTE SEL = 0 时,引脚用作三态门并行数字输入和输出引脚。 CS 和 RD 均为低电平时,输出 DB14 的转换结果;<br>当 PAR /SER/BYTE SEL = 0 ,且 DB15/BYTE SEL = 1 时,芯片进入<br>并行字节接口模式,HBEN 决定高位字节输出先后。若<br>HEBN=1,高位字节(MSB)先输出。<br>HEBN=0,低位字节(LSB)先输出。 |

| 33    | DO/DI | DB15/BYTE<br>SEL | 并行输出数据位 15(DB15)/并行字节模式选择(BYTE SEL)<br>当 PAR /SER/BYTE SEL = 0 时,引脚用作三态门并行数字输入和输<br>出引脚。 CS 和 RD 均为低电平时,输出 DB15 的转换结果;<br>当 PAR /SER/BYTE SEL = 1 时,BYTE SEL 决定芯片接口串并行模<br>式。该状态下,若<br>DB15/BYTE SEL=0,则为串行接口模式;<br>DB15/BYTE SEL=1,则为并行字节接口模式。   |

| 34    | DI    | REF<br>SELECT    | 内部/外部基准电压选择逻辑输入。如果此引脚设为 AVCC 电压时,则选择内部基准电压模式。如果此引脚设为逻辑低电平,则内部基准电压禁用,须使用外部基准电压。                                                                                                                                                                    |

| 36,39 | P     | REGCAP           | 去耦电容引脚,用于 1.9V 内部稳压器、模拟低压差(ALDO)和数字 低压差(DLDO)稳压器的电压输出。须连接 1μF 去耦电容至 AGND。                                                                                                                                                                         |

| 42    | AIO   | REFIN/<br>REFOUT | 基准电压输入(REFIN)/基准电压输出(REFOUT)。当 REF SELECT 引脚设置为逻辑高电平时,使用内部 2.5V 基准电压源; 当 REF SELECT 引脚设置为逻辑低电平时,内部基准禁用,可使用外部 2.5V 基准电压源。对于内部和外部基准电压源选项,从 REFIN 引脚到地都应采用 10μF 去耦电容(靠近 REFGND 引脚)。                                                                  |

| 43,46 | AI    | REFGND           | 基准电压接地引脚。均连接至 AGND。                                                                                                                                                                                                                               |

| 44,45 | AIO | REFCAPA,<br>REFCAPB | 基准电压缓冲输出。须将这些引脚连在一起,并通过低 ESR(有效串<br>联电阻) 10μF 陶瓷去耦电容至 AGND。引脚上的电压通常为 4.5 V。 |

|-------|-----|---------------------|-----------------------------------------------------------------------------|

| 49    | AI  | V1                  | 通道1模拟输入。                                                                    |

| 50    | AI  | V1GND               | 通道1模拟输入。                                                                    |

| 51    | AI  | V2                  | 通道2模拟输入。                                                                    |

| 52    | AI  | V2GND               | 通道2模拟输入。                                                                    |

| 引脚编号 | 引脚类型 | 引脚名称  | 引脚功能       |

|------|------|-------|------------|

| 53   | AI   | V3    | 通道3模拟输入。   |

| 54   | AI   | V3GND | 通道3模拟输入。   |

| 55   | AI   | V4    | 通道4模拟输入。   |

| 56   | AI   | V4GND | 通道4模拟输入。   |

| 57   | AI   | V5    | 通道 5 模拟输入。 |

| 58   | AI   | V5GND | 通道 5 模拟输入。 |

| 59   | AI   | V6    | 通道6模拟输入。   |

| 60   | AI   | V6GND | 通道6模拟输入。   |

| 61   | AI   | V7    | 通道7模拟输入。   |

| 62   | AI   | V7GND | 通道7模拟输入。   |

| 63   | AI   | V8    | 通道8模拟输入。   |

| 64   | AI   | V8GND | 通道8模拟输入。   |

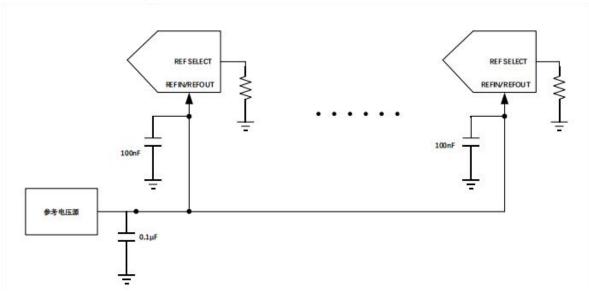

#### 内部/外部参考电压

FAD7606 有内部/外部两种参考电压模式,当 REF SELECT 引脚置高电平时,内部参考模式使能,内部基准源提供参考电压;当 REF SELECT 引脚置低电平时,内部参考禁用,可输入外部参考电压。

#### 外部参考模式

FAD7606 的外部参考模式配置如图9所示。

图 9 单个外部基准驱动多个 FAD7606 REFIN 引脚

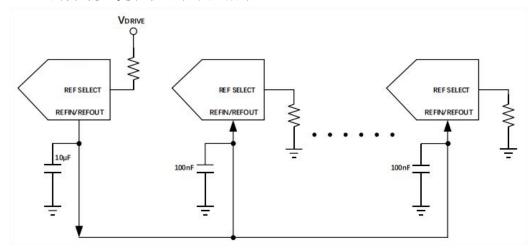

#### 内部参考模式

FAD7606的内部参考模式配置如图10所示。

图 10.内部基准驱动多个FAD7606 REFIN引脚

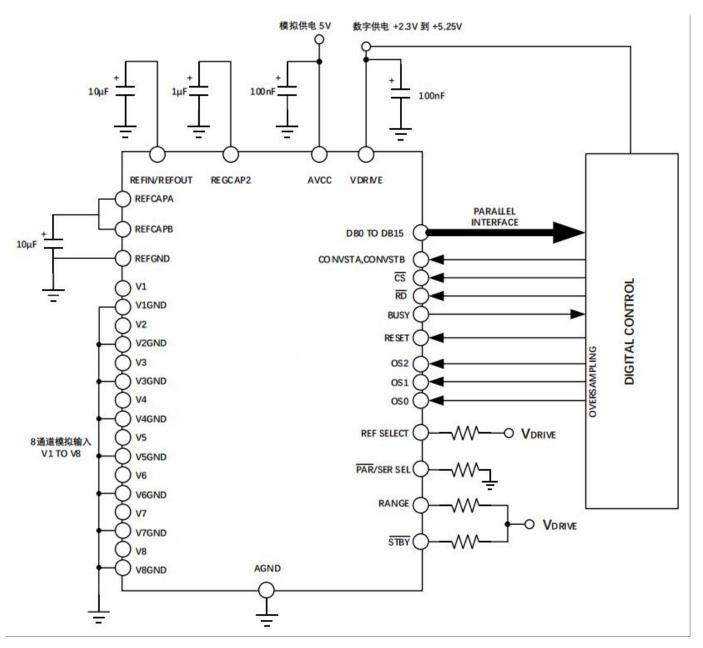

## 典型连接关系图

如图 11所示,该图为 FAD7606 的典型连接关系图。

图 11 FAD7606 典型连接关系图

#### 电源模式选择

FAD7606 有两种电源模式,分别是正常工作模式(±5V、±10V 输入)和省电模式(待机和 关断),由 STBY 和 RANGE 引脚控制,配置关系见表 7。

表 7 电源模式选择

| 电源模式      | STBY | RANGE |

|-----------|------|-------|

| 关断        | 0    | 0     |

| 待机        | 0    | 1     |

| ±5V 输入范围  | 1    | 0     |

| ±10V 输入范围 | 1    | 1     |

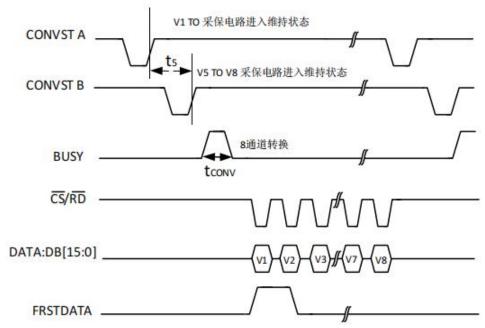

#### 转换控制

如图12所示,CONVST A 上升沿使 V1-V4 通道的采样保持电路进入保持模式,CONVST B上升沿使 V5-V8 通道采保电路进入保持模式,实现同步采样功能。当 CONVSTA 和 CONVSTB 的 上升沿均到来,转换过程开始。

BUSY信号表征转换过程,该信号下降沿时,采保电路回到采样模式,新的数据可以从DB[15:0]读出

图 12FAD7606使用独立的 CONVST A 和 CONVST B 信号时对通道集进行同步采样(并行模式)

#### 数字接口

FAD7606 有三种接口可选:并行接口,高速串行接口,并行字节接口。三种模式受PAR /SER/BYTE SEL 和 DB15/BYTE SEL 两组引脚控制,配置关系见表 8。

| PAR /SER/BYTE<br>SEL | DB 15 | 接口模式 |

|----------------------|-------|------|

| 0                    | 0     | 并行   |

| 1                    | 0     | 串行   |

| 1                    | 1     | 并行字节 |

表 8 接口模式选择

# 过采样编码模式

表 9展示过采样译码与过采样率的对应关系,以及FAD7606不同采样率下的 SNR 性能。

表 9 过采样编码

| OS[2:0] | OS Ratio | SNR 5V 范围<br>(dBFS) | SNR 10V 范围<br>(dBFS) | 3 dB BW 5V 范围<br>(kHz) | 3 dB BW 10V 范<br>范围(kHz) | 最高转换速率(kHz) |

|---------|----------|---------------------|----------------------|------------------------|--------------------------|-------------|

| 000     | No OS    | 86.0                | 86.5                 |                        |                          | 200         |

| 001     | 2        | 87.6                | 88.3                 |                        |                          | 100         |

| 010     | 4        | 89.5                | 90.0                 |                        |                          | 50          |

| 011     | 8        | 91.9                | 92.4                 |                        |                          | 25          |

| 100     | 16       | 93.7                | 94.2                 |                        |                          | 12.5        |

| 101     | 32       | 95. 1               | 95.4                 |                        |                          | 6.25        |

| 110     | 64       | 95.4                | 95.8                 |                        |                          | 3.125       |

| 111     | invalid  |                     |                      |                        |                          |             |

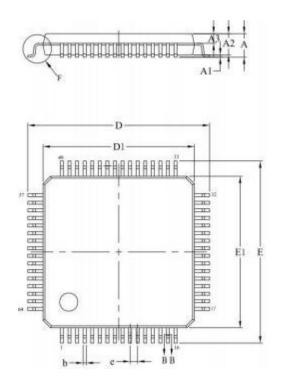

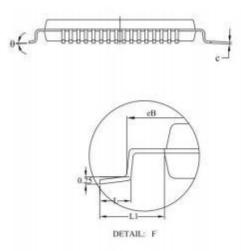

## 外形尺寸

| SYMBOL | MILLIMETER |         |       |  |  |

|--------|------------|---------|-------|--|--|

| SIMBOL | MIN        | NOM     | MAX   |  |  |

| A      | _          | _       | 1.60  |  |  |

| A1     | 0.05       | -       | 0.15  |  |  |

| A2     | 1.35       | 1.40    | 1.45  |  |  |

| A3     | 0.59       | 0.64    | 0.69  |  |  |

| b      | 0.18       | -       | 0.26  |  |  |

| bl     | 0.17       | 0.20    | 0.23  |  |  |

| c      | 0.13       |         | 0.17  |  |  |

| c1     | 0.12       | 0.13    | 0.14  |  |  |

| D      | 11.80      | 12.00   | 12.20 |  |  |

| D1     | 9.90       | 10.00   | 10.10 |  |  |

| E      | 11.80      | 12.00   | 12.20 |  |  |

| E1     | 9.90       | 10.00   | 10.10 |  |  |

| e      |            | 0.50BSC |       |  |  |

| eB     | 11.05      | _       | 11.25 |  |  |

| L      | 0.45       | -       | 0.75  |  |  |

| LI     | 1.00REF    |         |       |  |  |

| а      | 0          |         | 7*    |  |  |

图 13 64 脚 QFP 封装尺寸图

## 订购信息

#### 表 10 产品订购信息

| 型号      | 订单编号               | 温度范围     | 封装类型    | 包装形式 |

|---------|--------------------|----------|---------|------|

| FAD7606 | FAD7606YLQFP64G/TR | -40~85°C | LQFP-64 | Tray |

#### 声明

- 我公司保留说明书更改权利,恕不另行通知。

- 任何半导体产品在特定条件下都有一定的失效或发生故障的可能,买方有责任在使用我司产品进行系统设计和整机制造时遵守安全标准并采取安全措施,以避免潜在失败风险可能造成人身伤害或财产损失情况的发生!

- 产品品质的提升永无止境,我司将竭诚为客户提供更优秀的产品!

## 版本修改记录

| 版本编号          | 修改内容         |

|---------------|--------------|

| first edition |              |

| V1.0          | 1. 第20页更新声明。 |